系统厂商为何蜂拥做芯片?

系统厂商蜂拥自研芯片,有利于实现“系统+算法+软件+芯片”集成式优化的智能产品,这是目前算法和芯片技术决定的。未来终端智能的基础瓶颈在芯片研发成本,开源的指令集与开工工具,全自动EDA工具和先进封装工艺有望大幅降低芯片开发门槛,压缩开发时间并降低开发成本,推动终端智能的发展。

近年来,我们发现越来越多的系统厂商开始成立自己的芯片部门,开发并推出面向自有产品的芯片,以AI芯片和集成AI模块的SoC芯片为主。

图1. 系统厂商蜂拥做芯片

互联网厂商如阿里、百度和腾讯。阿里平头哥2018年成立后,2019年7、8、9月接连推出RISC-V处理器、SoC开发平台和AI云端推理芯片。百度在2018年7月推出云端AI训练和推理芯片后,2019年12月宣布将通过三星在2020年初量产。腾讯的参股公司燧原科技2019年12月发布云端AI训练芯片,将在腾讯云热启动。

手机厂商如小米、Vivo和OPPO。手机厂商除华为、苹果、三星较早开始自研芯片外,小米在2017年发布澎湃S1 SoC芯片。2019年,Vivo在11月发布联合三星开发的5G SoC芯片,OPPO预计明年发布协处理器M1。

电视厂商如创维、海信。2018年创维就发布了两款AI画质增强芯片,蜂鸟和变色龙。2019年,海信在7月成立青岛信芯,开展电视SoC和AI芯片研发。

这个现象,从晶圆制造厂的客户构成可以得到印证。根据Mentor和IC Insights的统计数据,2012年,系统厂商在晶圆厂的营收占比仅为2%,到2018年这个比例达到17%。近5年复合增长率达到70%,同期Fabless为6%,IDM厂为9%。可见,越来越多的系统厂商进入自研芯片市场。

图2. 晶圆厂营收构成

01

“系统+算法+软件+芯片”

出现系统厂商做芯片的现象,我们认为主要是因为当前理想的智能化需要针对特定场景,设计AI系统、算法和软件,再根据算法特点设计加速芯片。即“系统+算法+软件+芯片”的集成式优化,是实现高质量的AI应用的有效手段。

AI算法的泛化能力不足。

目前,AI算法需要依赖于应用场景,即研发人员需要根据各种边界条件确定来优化算法性能。如果更换一个场景,算法需要再调整。AI算法的泛化能力弱,导致只能实现定制化智能,限制了不同场景更大范围推广。

同时,AI算法是数据驱动的,特定场景需要大量的数据,在实际应用中还需要数据和算法的持续迭代优化,这个过程对技术、成本和运维要求较高。

AI芯片的优化依赖于与AI算法的协同优化。

目前,AI芯片开发需要软硬件协同优化基本是业界共识。早期,算法和硬件以单独优化为主。2009-2014年优化计算引擎,提高并行度;2014-2016年开始,随着模型规模方法,开始优化存储系统,但是,性能基本达到单独优化的极限。

理想的软硬件协同优化需要一种能够同时描述软件与硬件的语言,能够自动的实现功能划分,哪些在软件上运行,哪些在硬件上运行。但是,目前的系统复杂,功能划分多样,一般很难实现。

为实现一定程度的软硬件协同优化,有一些折衷的技术出现。如在芯片开发初期,可以通过ARM+NVDLA搭建一个简单的SoC虚拟原型,运行操作系统和NVDLA的inference实例,这允许软件开发人员运行AI算法。这个SoC原型成为软硬件开发的接口,通过软件工程师的反馈,硬件设计人员可以优化芯片架构和细节。

所以从技术链条看,场景产生数据,数据决定算法模型,算法模型决定芯片架构。因而,理想的智能化是定制化的。

这就容易理解为什么系统厂商纷纷入局,开发面向自己产品的AI芯片或+AI SoC芯片。同时,也有类似地平线这样开始做芯片的公司延伸做解决方案,也有云知声这样做AI平台的公司开始做芯片,都是为了打通“系统+算法+软件+芯片”的集成优化链条。

02

瓶颈在哪里?

未来,智能化需要向更多场景,更多设备扩散。

云端智能的瓶颈在算法。

目前,主要的云服务厂商都推出了自己的AI推理芯片,如亚马逊的Inferentia,阿里的含光800,微软的Brainwave,谷歌的TPU,腾讯的燧源(来自参股公司),华为的昇腾910等。除微软的Brainwave采用FPGA外,其他厂商都是ASIC芯片。ASIC芯片是针对特定应用的专用芯片,例如谷歌的TPU针对语音识别、图像识别和搜索应用做了优化,阿里平头哥的含光800针对语音识别、机器视觉、决策智能做了优化。

虽然ASIC芯片开发难度大,成本高,周期一般1-2年,失败概率大。但是随着算法的升级,云服务厂商有足够动力、财力和能力升级芯片。

因而,云端智能的瓶颈还是算法,无论是云服务厂商,还是使用AI云服务的下游厂商,优化自身算法、系统和服务都是核心。

终端智能的瓶颈在芯片。

虽然算法也是核心之一,但高成本的芯片研发费用,限制了众多有限智能场景的推广。

终端应用要求低功耗,算力优先的AI芯片一般选择使用先进制程。例如手机+AI SoC芯片都采用最先进的7nm工艺制造,特斯拉的车用AI芯片采用14nm工艺制造。

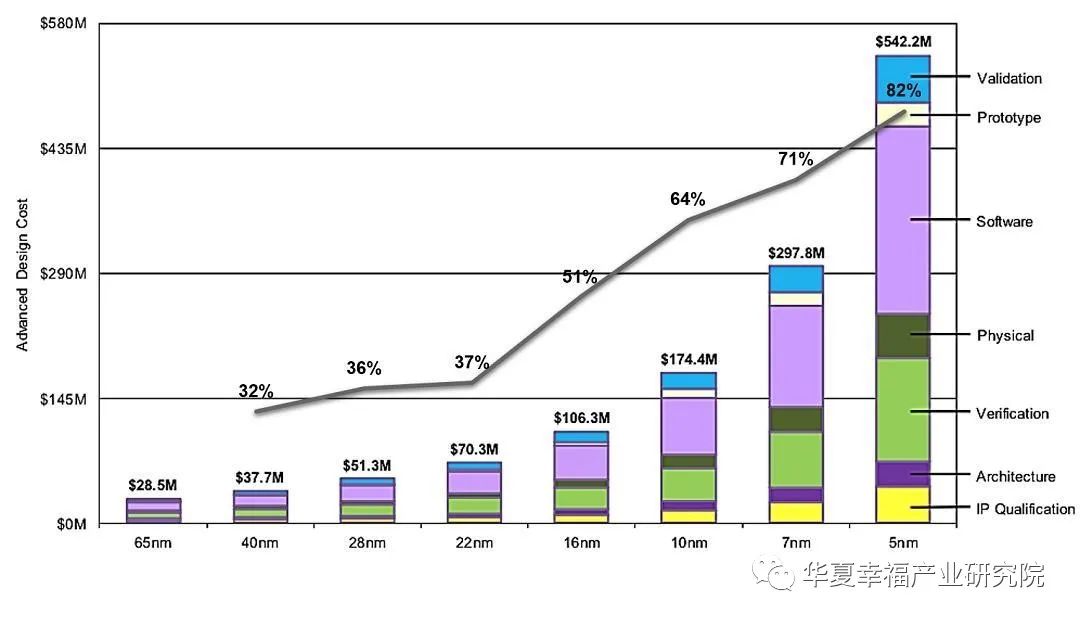

制程越先进,设计成本越高。芯片设计成本构成一般包括EDA软件、IP采购、芯片验证与流片、相关硬件和人力成本等。IBS数据显示,22nm制程之后每代技术设计成本增加均超过50%。设计一颗28nm SoC芯片成本约为5000万美元,而7nm则需要3亿美元,3nm的设计成本可能达到15亿美元。

图3. 先进制程下芯片设计成本大幅升级

数据来源:International Business Strategies

03

如何降低芯片成本?

目前有三个技术在朝着降低终端产品芯片成本的方向发展,分别是开源指令集、先进封装+chiplet模式和全自动EDA技术。

1、 开源指令集

RISC-V是一种简单、开源的精简指令集架构,于2010年主要由美国加州大学伯克利分校的团队发明。发明的初衷之一就是规避商业指令集(ARM、X86等)高昂的专利和授权费用,同时采用模块化设计,降低芯片设计门槛和开发时间。

RISC-V发展迅速。2015年成立等RISC-V基金会,目前包括108家会员单位,其中白金会员18家,普通会员90家,并且会员数量在持续高速增长。其中,多家中国大中型企业级科研机构也加入了基金会,如中兴、华为、杭州中天、中科院计算所等。

我国力推RISC-V指令集。2018年9月,中国RISC-V产业联盟在上海成立,吸引了芯原控股、芯来科技、杭州中天微、北京君正等多家单位加入。同年11月,中国开放指令生态联盟成立,发起单位包括中科院计算所、北京大学、阿里-中天微、百度、中芯国际等近20家研究机构和企业,旨在构建指令集、架构、芯片、软件、整机应用等RISC-V产业链。

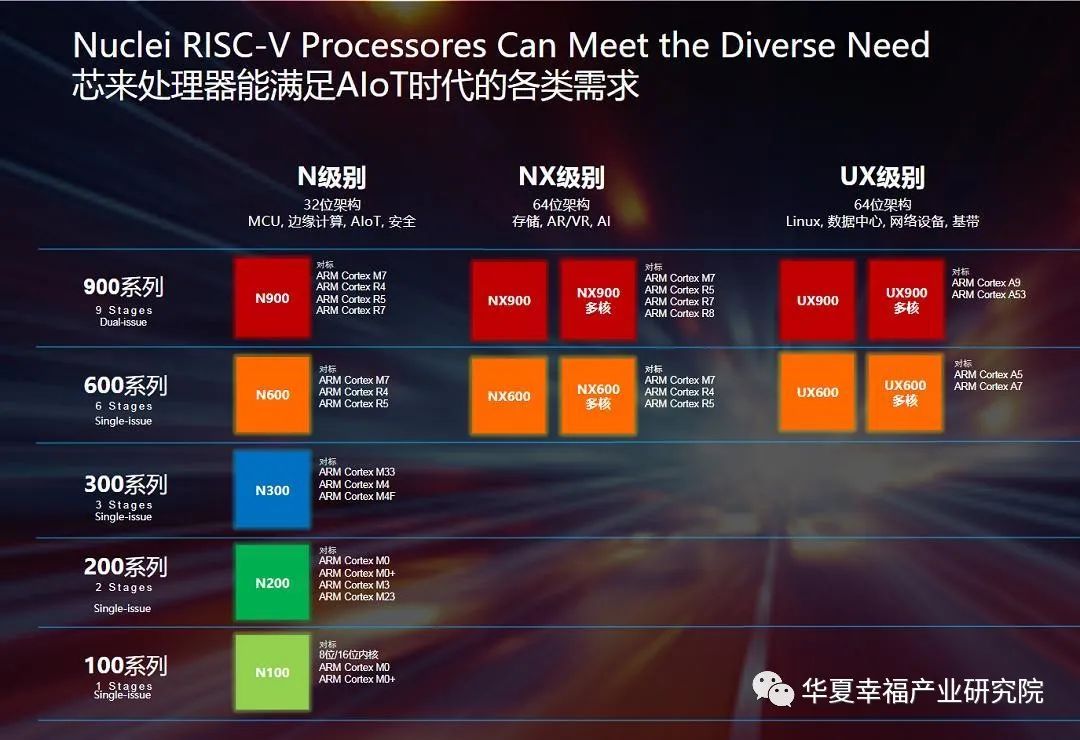

近两年,RISC-V生态逐步完善,芯片种类越发丰富。以国内创企芯来科技为例,公司目前可以提供对标ARM M0-A55芯片的RISC-V MCU IP,面向边缘计算、安全、存储等多种场景。在性能可比的情况下,相对ARM芯片可以节约30%-50%成本。同时,阿里平头哥也在2019年7月推出了RISC-V处理器玄铁910,还有北京君正、晶心科技等都有类似产品推出。

图4. 芯来科技产品线

图片来源:芯来科技官网

AI芯片方面,也有RISC-V芯片上市。2018年9月,华米科技推出了基于RISC-V的+AI SoC芯片黄山1号。2019年6月,该芯片已经在华米智能手表上量产。AI模块负责实现心脏生物特征识别引擎、心律异常监测引擎等功能。

RISC-V模块化的设计可以缩短芯片开发周期,开源生态可以降低开发成本,可以预见,未来RISC-V芯片必将在边缘计算和终端智能领域发会更大作用。

2、 先进封装+Chiplet模式

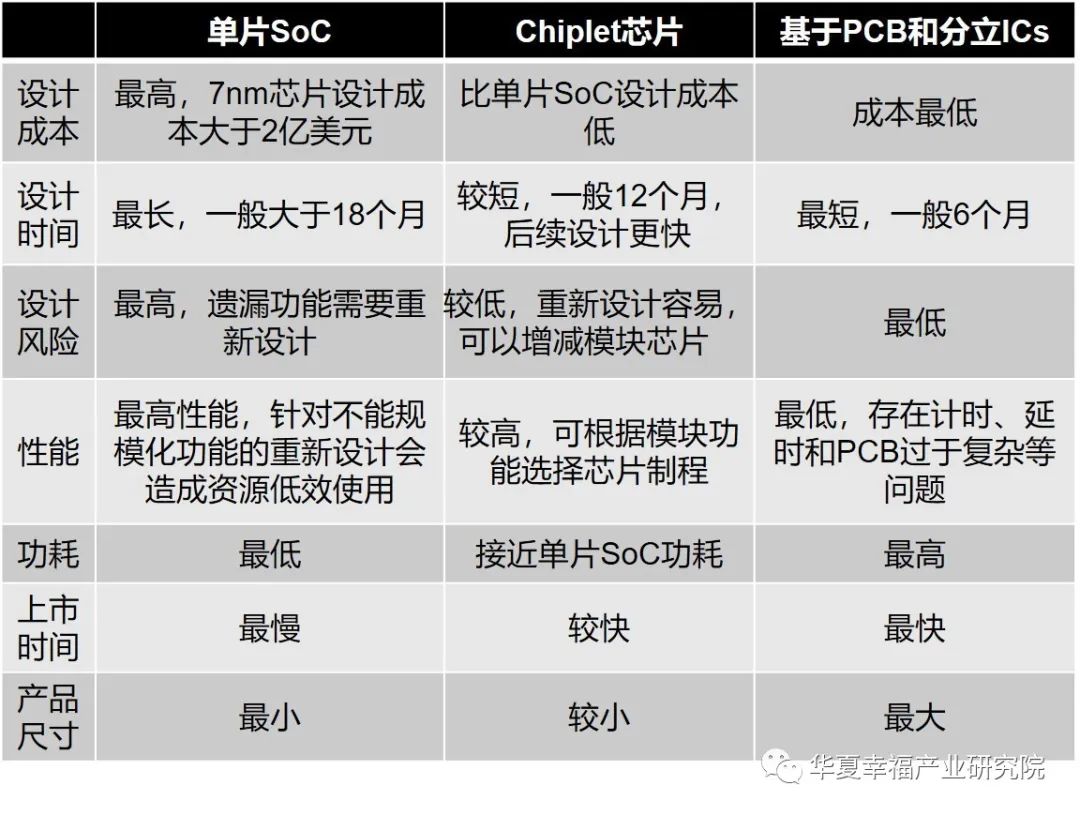

终端智能一般以+AI SoC芯片形式出现,集成了MCU、AI加速模块、存储、I/O等。目前,英特尔、台积电等多企业开始在推广chiplet模式,有望使SoC芯片开发成本降低、开发时间缩短、开发风险降低。

Chiplet,直译为小芯片或芯粒,是一类满足特定功能的die。Chiplet模式是通过die-to-die内部互联技术将多个模块芯片与底层基础芯片封装在一起,构成多功能的异构System in Packages芯片。

图5. Chiplet芯片相对单片SoC和基于PCB的集成技术的优缺点

数据来源:Semico Research,华夏幸福产业研究院

Chiplet模式的玩家致力于构建一个生态,这里有一个丰富的Chiplet库可供选择,这些die既可以是逻辑,也可以是模拟的,可以来自不同工艺制程;集成商根据需求设计芯片架构,自由选择Chiplet芯片交给制造商进行制造和封装,快速低成本的实现SoC芯片的产出。

发展Chiplet模式面临多种技术挑战。如die-to-die的数据互联标准问题,目前来自英特尔的AIB标准已经免费开放,以支持Chiplet生态系统建设,包括设计方法或服务供应商、代工厂、封装厂和系统供应商。另外,封装技术、芯片测试技术和开发工具问题,还需要进一步完善。更详细的内容,可以查看作者的文章《像搭积木一样造芯片?》。

目前,英特尔、台积电已经推出了自己的Chiplet芯片,还有相关创企已经开始Chiplet模式的实践。相信,Chiplet模式定会催生新的商业模式和新的产业增长点。

值得一提的是,AI芯片非常适用于Chiplet模式。因为在现有算法框架下,AI芯片专做AI加速,在Chiplet模式下,可以与CPU、存储、传感、数模转换等芯片共存,不同工艺实现很好的兼容,同时更好优化成本。

3、全自动EDA技术

如果把芯片设计和程序开发类比,芯片设计的自动化水平是很低的。

程序开发通常可以使用统一的编译器,实现高级编程语言与底层机器码的转换。但是,芯片设计中的版图设计(layout)通常需要人工实现,虽然有EDA工具可以部分辅助人工绘制版图,但这个过程依然非常耗时,需要较深专业技能和大量经验来实现。

同时,程序开发中通常由很多开源程序包可以使用,如Python、R语言,非常节省开发时间。但是,芯片开发领域,设计复用非常少,因为目前尚没有通用的电路标准格式。

美国DARPA从2017年开始推动的两个EDA项目旨在解决上面的问题。

IDEA (Intelligent Design of Electronic Assets)项目旨在实现一个全自动芯片版图生成器,使具有有限电子设计专业知识的用户,能够在24小时内完成电子硬件的物理设计。

POSH(Posh Open Source Hardware)项目旨在发展可持续的开源硬件生态,以及相应的验证工具,同时提供一个开源硬件基础模组库,让大家可以自由调用模组库里的模块,避免重复设计问题。

同时,业界积极推进的EDA+AI技术,目前已经处于主动推荐阶段,未来几年有望进入全自动化阶段,即基于系统需求,自动实现芯片设计、封装和电路板的自动化设计。值得一提的是,这个阶段需要上述两个项目的支持。

图6. AI赋能EDA技术路线图

结语

何时能实现全面智能化?也许是,当设计芯片像开发程序一样简单,制造芯片像搭积木一样灵活的时候。

当下,新冠肺炎疫情仍在持续。种种隔离之下,整个社会对智能化产品、云端应用的需求从未有这样迫切。毫无疑问,这场终将散去的瘟疫将会大大加速智能社会、数字社会的进程,激发终端智能的需求。

技术已经路上,我们期待全面智能化的到来!

下一篇:三大趋势性变化,商办新路在何方